Sequential Logic

Output จะขึ้นกับ

1. Input ขณะนั้น

2. Input ก่อนหน้า

3. Output ก่อนหน้า

แบบ NOR Gate

แบบ NAND Gate

Flip-Flop

เป็นอุกปกรณ์พื้นฐานทาง Sequential Logic

มี Output คือ Q และ Q'

SR Flip-Flop

แบบ NOR Gate

แบบ NAND Gate

เป็น Invert กับแบบ NOR

Gate

D Type Flip-Flop

T Type Flip-Flop

เมื่อมีสัญญาณ Clock เข้ามา ถ้า T เป็น “1” Q กับ Q' จะสลับกัน

ถ้า T เป็น “0” Q กับ Q' จะคงเดิม

JK Flip-Flop

เปรียบเสมือนเอา Flip-Flop แบบ D Type กับ

T Type มารวมกัน

Asynchronous Counter

คือแบบที่ Output Stage ของ Flip-Flop แต่ละตัวเปลี่ยน Stage ไม่พร้อมกัน

ข้อดี : สร้างง่าย

ข้อเสีย : ความเร็วจากการสะสม

Propagation

Delay จาก Gate แต่ละตัว

และมี Ripper Effect

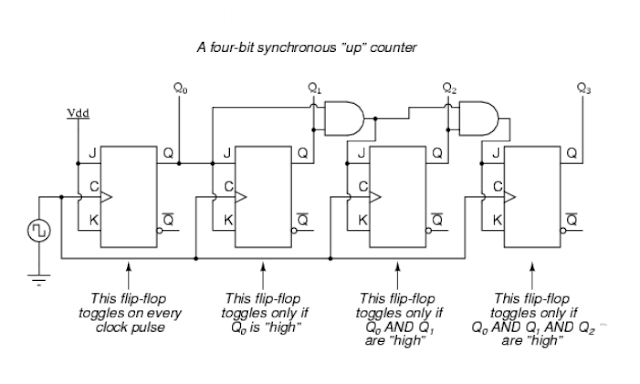

Synchronous Counter

คือแบบที่ Output Stage ของ Flip-Flop แต่ละตัวเปลี่ยน Stage พร้อมกัน

เกิดจากการนำ D Type Flip-Flop มาต่อกัน

เพื่อใช้จัดเก็บหรือส่งข้อมูลในรูปเลขฐาน 2 มีหลักๆอยู่ 4 แบบ คือ

Serial-in to Serial-out (SISO)

Serial-in to Parallel-out (SIPO)

Parallel-in to Parallel-out (PIPO)

Parallel-in to Serial-out (PISO)

ตอนเรียนในคาบยังไม่ค่อยเข้าใจ ต้องลองต่อวงจรดู

และไปศึกษาเพิ่มเติม ถึงจะเริ่มเข้าใจขึ้น

0 ความคิดเห็น:

Post a Comment